Is Mux A Combinational Circuit

Verilog code for 2:1 multiplexer (mux) Mux circuit innovative blood multiplexers Digital combinational logic part-iv

Innovative Blood: Multiplexers

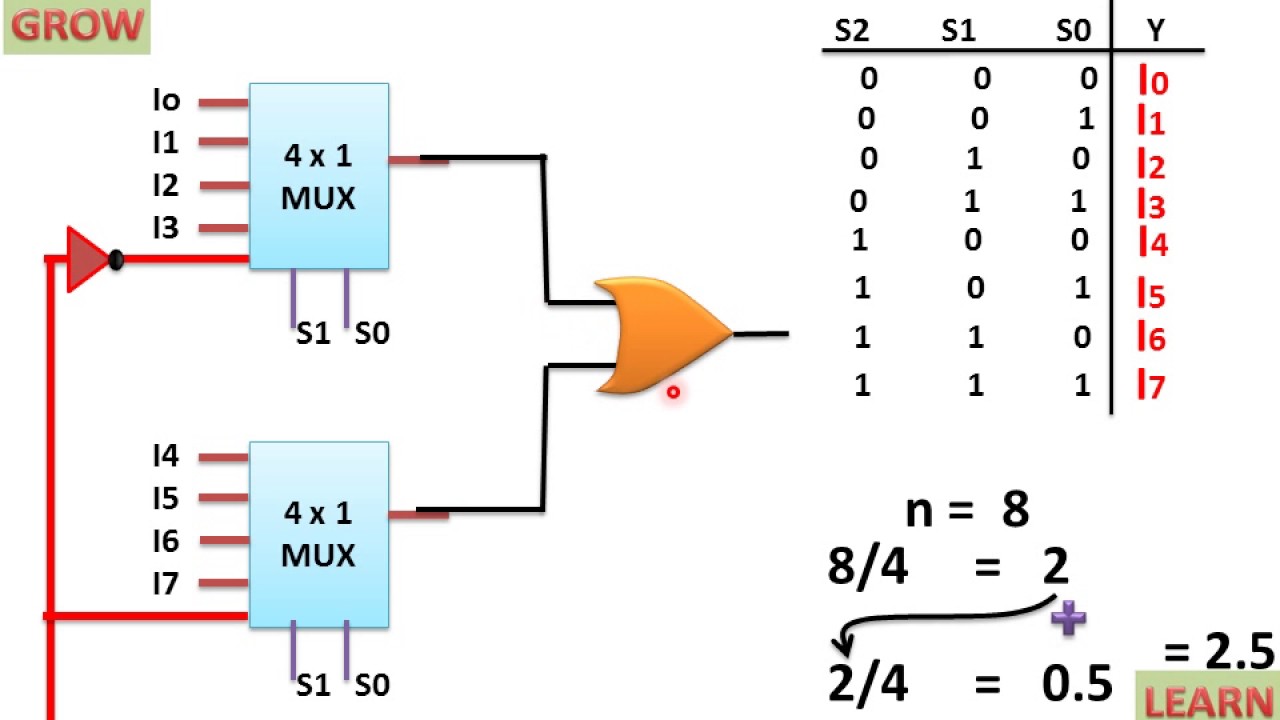

8x1 mux logic diagram : using 8 1 multiplexers to implement logical Circuit mux circuitlab description 8x1 mux multiplexer logic combinational table

Mux multiplexer 8x1 diagram logic schematic using input table 16 vlsi truth 2x1 symbol muxes figure structure eda elcho

Mux multiplexer 4x1 cmosDifference between multiplexer and demultiplexer (with operational 8 to 1 mux using 4 to 1 mux by two different methods, combinational16:1 mux : vlsi n eda.

Developed 8 to 1 multiplexer diagram and truth tableDigital electronics Mux multiplexer multiplexers enable output examradar logic disabled electronicsPos multiplexer slideserve map ppt powerpoint presentation.

Mux multiplexer verilog logic 2x1

Multiplexer mux circuit diagram truth electronics inputs nand gates boolean multiplexing combination given elcho2 to 1 mux circuit Multiplexer demultiplexer mux circuit difference demux between output input signals provide control single order figureCombinational logic mux circuits.

Mux using digital differentInnovative blood: multiplexers Mux 8x1 multiplexer 4x1 implementation logic implement multiplexers 2x1 logicalCombinational logic circuits : definition, examples, and applications.

Mux multiplexer multiplexers multiplexing activated strobe

8x1 mux logic diagram / 8x1 mux logic diagramMultiplexer inputs lines Multiplexer (mux) and multiplexingWhat is a multiplexer? operation, types and applications.

.

PPT - POS, K-map and Multiplexer PowerPoint Presentation, free download

2 to 1 Mux Circuit - CircuitLab

8 to 1 MUX using 4 to 1 MUX by two different Methods, Combinational

8X1 Mux Logic Diagram : Using 8 1 Multiplexers To Implement Logical

Innovative Blood: Multiplexers

What is a multiplexer? Operation, types and applications

Verilog code for 2:1 Multiplexer (MUX) - All modeling styles

Combinational Logic Circuits : Definition, Examples, and Applications

Digital Combinational Logic Part-IV